VHDL Entwicklung

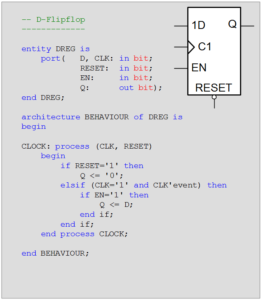

Unser Unternehmen ist seit Jahrzehnten aktiv in der FPGA-Entwicklung und bietet umfassende Expertise in diesem Bereich. Unsere hochqualifizierten Experten setzen die Very High Speed Integrated Circuit Hardware Description Language (VHDL) ein, um leistungsstarke und maßgeschneiderte Logikbausteine für eine Vielzahl von Herstellern zu entwickeln.

Wir beschäftigen uns intensiv mit den neuesten Technologien und Trends der FPGA-Entwicklung und nutzen unsere Erfahrung, um moderne, effiziente Lösungen in VHDL zu realisieren. FPGA-Designs stellen eine ideale Antwort auf viele technische Herausforderungen dar, da sie ein exzellentes Preis-Leistungs-Verhältnis bieten. Dank unserer Kompetenz können wir innovative, kundenspezifische Lösungen entwickeln, die durch die Implementierung präzise abgestimmter VHDL-Modelle überzeugen.

Unsere Experten verstehen es, die neuesten FPGA-Technologien zu nutzen, einschließlich leistungsstarker Typen, die integrierte CPU-Kerne enthalten. Dies ermöglicht uns, hochkomplexe System-on-a-Chip (SoC)-Designs effizient zu realisieren und die Entwicklungszeit erheblich zu verkürzen.

Mit unserem tiefgreifenden Fachwissen und unserer Leidenschaft für innovative Technologien begleiten wir Sie durch den gesamten Entwicklungsprozess – von der ersten Idee bis hin zu einer maßgeschneiderten, einsatzbereiten Lösung.

Wir bieten auch VHDL Schulungen an.

FPGA Hersteller und Produkte

Die FPGA-Branche hat in der jüngerer Zeit durch Übernahmen und die damit einhergehende Marktkonzentration auf sich aufmerksam gemacht. Wir verwenden hauptsächlich Logikbausteine der Firmen Intel/Altera, AMD/Xilinx, Lattice und Microchip/Actel und programmieren diese vorwiegend in VHDL.

Intel

Intel übernahm Altera im Jahr 2015, und seitdem werden die Altera-Produkte zunehmend als Intel® FPGAs vermarktet. Diese bieten ein umfangreiches Portfolio an leistungsstarken, programmierbaren Logikbausteinen.

AMD

AMD übernahm im Jahre 2022 die Firma Xilinx, den weltgrößten Entwickler und Hersteller von FPGAs und vermarktet deren Produkte seitdem unter eigenem Namen. In der Hauptsache wurden derzeit vier Bausteinfamilien gefertigt: einfache Logik (Coolrunner), FPGAs im Niedrigpreissegment (Spartan), im mittleren Leistungsbereich (Artix, Kintex) und für Hochleistungsanwendungen (Virtex).

Lattice

Für weniger komplexe Systeme oder Baugruppen mit begrenztem Platzangebot bieten sich die iCE-Serien von Lattice an, deren Bausteine auch in geringen Stückzahlen kosteneffektiv sind und integrierte I2C- und SPI-Cores besitzen.

Cologne Chip

Neu in den Markt eingetreten ist das Deutsche Unternehmen Cologne Chip AG mit den GateMate FPGAs.

Diese Bausteine sind in einer einer ähnlichen Leistungsklasse wie etwa Intel Cyclone und Lattice iCE angesiedelt. Sie sind für manche Anwendungen aufgrund interessanter Detaillösungen und Funktionen besonders geeignet. Die gute Unterstützung durch Open Source Entwicklungstools kann ein entscheidender Pluspunkt für die Auswahl gerade dieser Chips sein.

FPGA Entwicklung

FPGAs waren historisch gesehen flexible, aber teure Lösungen für die Umsetzung komplexer Schaltlogik. Mit der wachsenden Komplexität und dem damit einhergehenden Preisverfall der ICs bei gleichzeitig steigender Leistungsfähigkeit hat sich dieses Bild gewandelt. FPGAs lassen sich hervorragend dort einsetzen, wo klassische Mikrocontroller nicht schnell oder zeitsynchron genug reagieren können.

Unsere Produkte wie z.B. das Tracii XL 2.0 nutzen diese Technologie, um hohe Leistung und Zuverlässigkeit zu gewährleisten. Die Verwendung von VHDL als Hardwarebeschreibungssprache ermöglicht es, auch komplexe Probleme effizient zu lösen. Wir verwenden dabei Entwicklungsumgebungen wie Intel Quartus für Altera-Designs und Vivado von AMD/Xilinx.

Mit Yosys, GHDL, Nextpnr, OpenFPGALoader etc. sind Open Source Werkzeuge entstanden, die sich insbesondere zur FPGA-Entwicklung für die Produkte von Lattice iCE und CologneChip GateMate anbieten.

VUnit mit VCL, Random und die „Open Source VHDL Verification Methodology“ OSVVM erlaubt eine zügige Umsetzung von Systemtests.

Ihre individuelle CPU

Leistungsfähige EPLDs bieten faszinierende Möglichkeiten für kundenspezifische Lösungen. Mit Intel/Altera FPGAs der Cyclone-, Arria- und Stratix-Serien lassen sich mehrere Prozessoren auf einem einzigen FPGA implementieren. Diese FPGAs bieten hohe Leistung und Flexibilität für Ihre spezifischen Anwendungen.

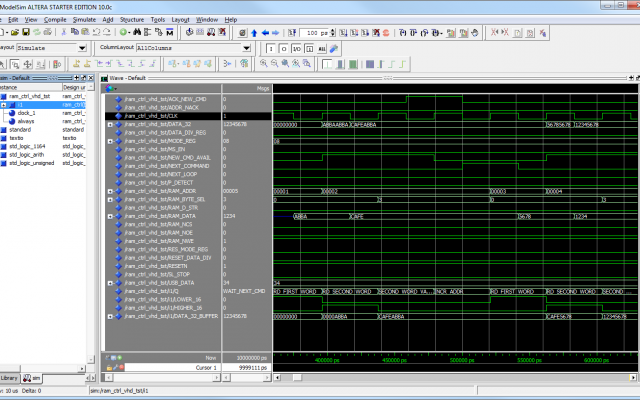

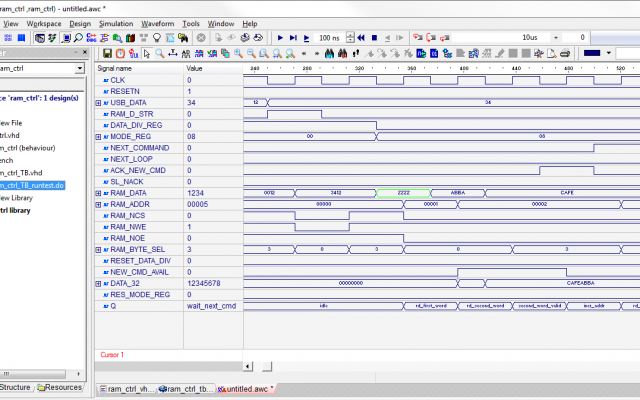

Testbenches

Die Entwicklung von Testbenches ist entscheidend für die Validierung von VHDL-Designs. Wir implementieren umfassende Testfälle, die mit leistungsfähiger Simulationssoftware wie Modelsim oder Active-HDL durchgeführt werden, um eine hohe Zuverlässigkeit unserer Designs zu garantieren.

Dauerhaft gespeicherte Konfiguration

Moderne Flash-FPGAs von Actel und Intel/Altera halten ihre Konfiguration auch ohne externe Speichermedien persistent, was sie ideal für sicherheitskritische Anwendungen macht.

Sichere Updates

Diese FPGAs lassen sich im Feld aktualisieren, was bedeutet, dass Sie Ihre Systeme sicher und effizient auf dem neuesten Stand halten können, ohne dass Dritte Zugriff auf die Programmierung haben.

- Sie benötigen professionelle Unterstützung im Bereich der Auswahl, Integration oder der Programmierung moderner Logikbausteine?

- telos ist seit 1988 aktiv. Nutzen Sie unser Ingenieurteam und die Erfahrung mehrerer Jahrzehnte!

- Nehmen Sie bitte Kontakt mit uns auf 040 450173 60

- Gerne auch für einen unverbindlichen "Klönschnack", wie man im Norden sagt